# VSBC-32

## Combined VMEbus System Controller and Serial Communications Controller Board

Manual ID 21168, Rev. Index 04 Jul 00

The product described in this manual is in compliance with all applied CE standards.

# **Revision History**

| Manual/Product Title: |                                                                                                                    | VSBC-32                                                                                                                                                                                                             |                    |                  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|--|

| Manual ID Number:     |                                                                                                                    | 21168                                                                                                                                                                                                               |                    |                  |  |

| Rev.<br>Index         | Brief Description o                                                                                                | f Changes                                                                                                                                                                                                           | <b>Board Index</b> | Date of<br>Issue |  |

| 0100                  | Initial Issue                                                                                                      |                                                                                                                                                                                                                     | 00/1               | Aug 95           |  |

| 0200                  | General corrections                                                                                                |                                                                                                                                                                                                                     | 00/2               | Dec 95           |  |

| 0201                  | J9 default setting ch                                                                                              | anged                                                                                                                                                                                                               | 00/2               | Nov 96           |  |

| 0300                  | General corrections                                                                                                | and new manual structure                                                                                                                                                                                            | 01                 | Dec 96           |  |

| 0301                  | New Preface                                                                                                        |                                                                                                                                                                                                                     | 01                 | Aug 98           |  |

| 0311                  |                                                                                                                    | 2.1.3. In Appendices, correc-<br>ses on pages MEM-2 to<br>-5 replaced.                                                                                                                                              | 01                 | Sept 98          |  |

| 04                    | adequate manual stru<br>backs mentioned, de<br>and communications<br>function-related boa<br>nology (e.g. processo | a Sheets 0100_1/2 integrated,<br>acture, new memory piggy-<br>scription of combined system<br>controller fucntionality,<br>rd diagrams, coherent termi-<br>or and board variant names)<br>lified, updated, reduced. | 01                 | July 00          |  |

# Imprint

Copyright © 2000 PEP Modular Computers GmbH. All rights reserved. This manual may not be copied, photocopied, reproduced, translated or converted to any electronic or machinereadable form in whole or in part without prior written approval of **Modular Computers** PEP Modular Computers GmbH.

#### **Disclaimer:**

PEP Modular Computers GmbH rejects any liability for the correctnesss and completeness of this manual as well as its suitability for any particular purpose.

This manual was realized by: TPD/Engineering, PEP Modular Computers GmbH.

# Contents

# Preface

| Preface                                     | ix   |

|---------------------------------------------|------|

| Proprietary Note                            | ix   |

| Trademarks                                  | ix   |

| Explanation of Symbols                      | x    |

| For Your Safety                             | xi   |

| High Voltage Safety Instructions            | xi   |

| Special Handling and Unpacking Instructions | xi   |

| General Instructions on Usage               | xii  |

| Two Year Warranty                           | xiii |

# Chapter 1

| 1.  | Intro | duction                                        | 1 - 3 |

|-----|-------|------------------------------------------------|-------|

| 1.1 | Sys   | tem Overview                                   | 1 - 3 |

| 1.2 | Boa   | rd Overview                                    | 1 - 4 |

| 1.  | 2.1   | Board-Specific Information                     | 1 - 4 |

| 1.  | 2.2   | Board Variants                                 | 1 - 4 |

| 1.  | 2.3   | Board Connectivity and Interface Expandibility | 1 - 5 |

| 1.  | 2.4   | Memory Piggybacks                              | 1 - 6 |

| 1.  | 2.5   | System-Relevant Information                    | 1 - 6 |

| 1.3 | Boa   | rd Diagrams                                    | 1 - 8 |

| 1.  | 3.1   | System-Level Functional Block Diagram          | 1 - 8 |

| 1.  | 3.2   | Frontpanels                                    | 1 - 9 |

| 1.  | 3.3   | Board Layouts 1                                | - 10  |

| 1.4 | Tec   | hnical Specifications1                         | - 12  |

| 1.5 Арр  | olied Standards 1 - 14                        |

|----------|-----------------------------------------------|

| 1.5.1    | CE Compliance 1 - 14                          |

| 1.5.2    | Mechanical Compliance 1 - 14                  |

| 1.5.3    | Environmental Tests 1 - 14                    |

| 1.6 Rela | ated Publications                             |

| 1.6.1    | VMEbus/CXC Systems/Boards 1 - 15              |

| 1.6.2    | Manufacturers' Component Documentation 1 - 15 |

| 2.  | Fund | ctional Description                                                   |

|-----|------|-----------------------------------------------------------------------|

| 2.1 | Gen  | neral Information                                                     |

| 2.2 | Spe  | ecifics                                                               |

| 2.  | 2.1  | System Control Functionality 2 - 4                                    |

| 2.  | 2.2  | Memory Configurations 2 - 5                                           |

| 2.  | 2.3  | DMA Channels 2 - 6                                                    |

| 2.  | 2.4  | Serial Communications Control 2 - 7                                   |

| 2.3 | Fun  | ctional Block Diagram2 - 10                                           |

| 2.4 | Boa  | rd Interfaces                                                         |

| 2.  | 4.1  | Serial I/O Interfaces 2 - 11                                          |

| 2.  | 4.2  | Piggyback Interface Connectors for Serial Interface Piggybacks 2 - 12 |

| 2.  | 4.3  | Memory Piggyback Interface Connectors 2 - 12                          |

| 2.  | 4.4  | EPROM DIP Sockets 2 - 12                                              |

| 2.  | 4.5  | Background Debug Mode Interface Connector 2 - 13                      |

| 2.  | 4.6  | VMEbus Backplane Interface 2 - 13                                     |

| 2.  | 4.7  | CXC Mezzanine Interface 2 - 14                                        |

| 2.5 | VSE  | 3C-to-VSBC-32 System Upgrading2 - 15                                  |

| 2.6 | Spe  | cial Board Functions                                                  |

| 2.  | 6.1  | Real-Time Clock 2 - 18                                                |

| 2.  | 6.2  | EEPROM                                                                |

| 2.  | 6.3  | PLL Operation Mode 2 - 18                                             |

| 2.  | 6.4  | Tick Generator                                                        |

| 2.  | 6.5  | Bus Error Timers                                                      |

| 2.6.  | 6         | Watchdog Timer          | 2 - 20 |

|-------|-----------|-------------------------|--------|

| 2.6.  | 7         | Reset Sources           | 2 - 20 |

| 2.6.  | 8         | "Slot 1" Detection      | 2 - 20 |

| 2.7 F | -<br>Fron | tpanel Functions        | 2 - 21 |

| 2.8 F | RTC       | and SRAM Data Retention | 2 - 21 |

| 2.9 A | Addı      | ress Decoder            | 2 - 23 |

| 2.9.  | 1         | Basic Structure         | 2 - 23 |

| 2.9.  | 2         | Boot Decoding           | 2 - 23 |

| З.  | Installation                         | 3 - 3 |

|-----|--------------------------------------|-------|

| 3.1 | Hardware Installation                | 3 - 3 |

| З.  | 1.1 External Serial Interface Module | 3 - 4 |

| 3.2 | Software Installation                | 3 - 4 |

| 4.  | Conf | iguration                      | 4 - 3 |

|-----|------|--------------------------------|-------|

| 4.1 | Hard | dware Configuration            | 4 - 3 |

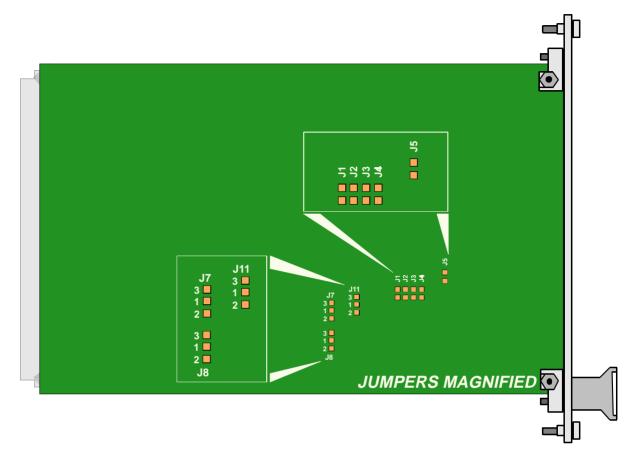

| 4.  | 1.1  | Wire Jumpers                   | 4 - 3 |

| 4.  | 1.2  | Solder Jumpers                 | 4 - 4 |

| 4.2 | Soft | ware Configuration             | 4 - 5 |

| 4.  | 2.1  | Address Map                    | 4 - 5 |

| 4.  | 2.2  | Board Control/Status Register  | 4 - 6 |

| 4.  | 2.3  | VMEbus Control/Status Register | 4 - 7 |

| 4.  | 2.4  | VMEbus Interrupt Mask Register | 4 - 8 |

|     |      |                                |       |

Аррх. А

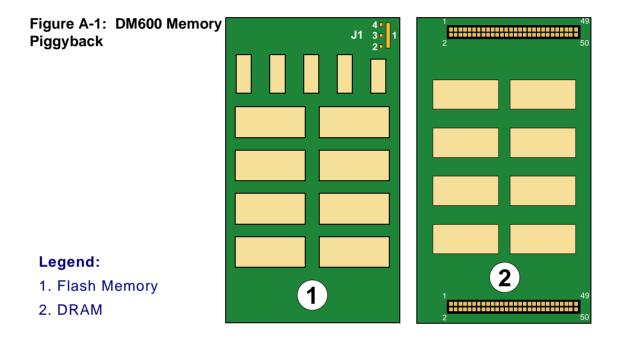

| А.  | Men | nory Piggybacks                        | A - 3 |

|-----|-----|----------------------------------------|-------|

| A.1 | Ger | neral                                  | A - 3 |

| A.2 | DM  | 600                                    | A - 4 |

| Α.  | 2.1 | Board Layout and Jumper Location       | A - 4 |

| Α.  | 2.2 | Jumper Description and Flash Addresses | A - 4 |

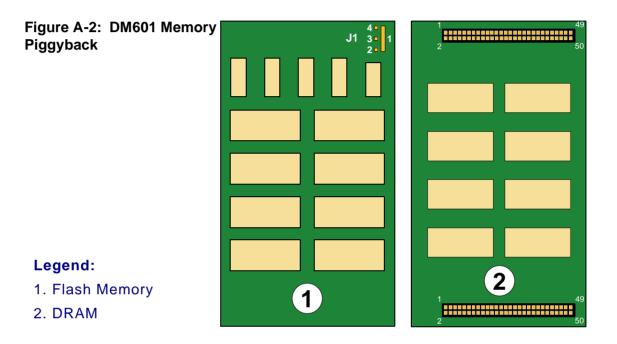

| A.3 | DM  | 601                                    | A - 5 |

| Α.  | 3.1 | Board Layout and Jumper Location       | A - 5 |

| А.  | 3.2 | Jumper Description and Flash Addresses | A - 5 |

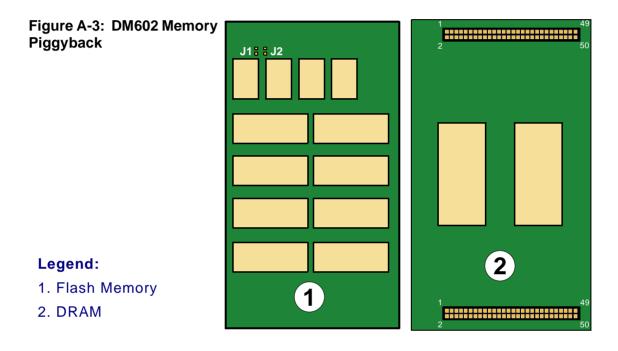

| A.4 | DM  | 602                                    | A - 6 |

| А.  | 4.1 | Board Layout and Jumper Location       | A - 6 |

| Α.  | 4.2 | Jumper Description and Flash Addresses | A - 6 |

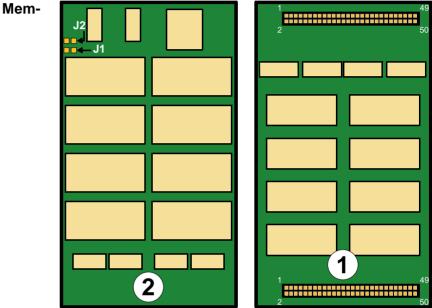

| A.5 | DM  | 603                                    | A - 7 |

| А.  | 5.1 | Board Layout and Jumper Location       | A - 7 |

| А.  | 5.2 | Jumper Description and Flash Addresses | A - 7 |

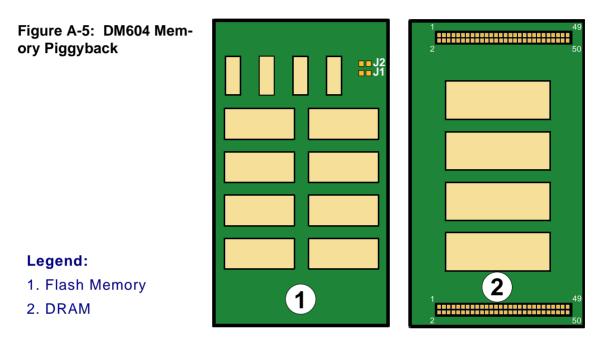

| A.6 | DM  | 604                                    | A - 8 |

| А.  | 6.1 | Board Layout and Jumper Location       | A - 8 |

| А.  | 6.2 | Jumper Description and Flash Addresses | A - 8 |

| A.7 | DM  | 605                                    | A - 9 |

| А.  | 7.1 | Board Layout and Jumper Location       | A - 9 |

| А.  | 7.2 | Jumper Description and Flash Addresses | A - 9 |

## Contents

| Аррх. | B |

|-------|---|

|       |   |

| В.  | Seria | al Interface Piggybacks                      | В-З    |

|-----|-------|----------------------------------------------|--------|

| B.1 | Gen   | neral                                        | В-З    |

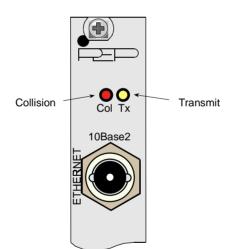

| В.2 | SI-1  | 0B2                                          | B - 4  |

| В.  | 2.1   | Specifications                               | B - 4  |

| В.  | 2.2   | Front Panel View                             | B - 4  |

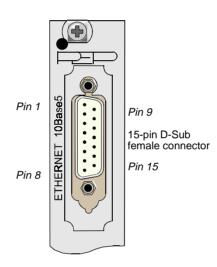

| В.З | SI-1  | 0B5                                          | B - 5  |

| В.  | 3.1   | Specifications                               | B - 5  |

| В.  | 3.2   | Front Panel View and Pinout                  | B - 5  |

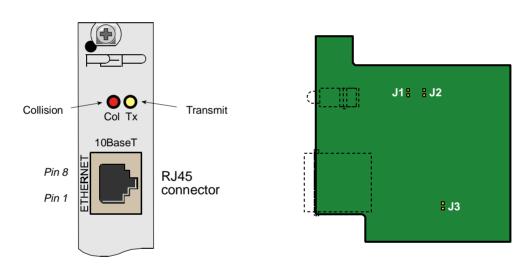

| B.4 | SI-1  | 0BT                                          | В-6    |

| В.  | 4.1   | Specifications                               | В-6    |

| В.  | 4.2   | Front Panel View, Jumper Layout, and Pinouts | B - 6  |

| 4.  | 2.1   | SI-10BT Jumper Settings                      | B - 7  |

| B.5 | SI-F  | PB232                                        | B - 8  |

| В.  | 5.1   | Front Panel View and Pinout                  | B - 8  |

| B.6 | SI-F  | PB485-ISO                                    | В-9    |

| В.  | 6.1   | Specifications                               | В-9    |

| В.  | 6.2   | Front Panel View, Jumper Layout, and Pinout  | В-9    |

| В.  | 6.3   | SI-PB485-ISO Jumper Settings                 | 3 - 10 |

# Аррх. С

| С.         | CXC                        | C - 3 |

|------------|----------------------------|-------|

| C.1        | CXC Address Ranges         | C - 3 |

| С.2        | CXC Generic Pinouts        | C - 5 |

| С.3        | CPU Pinout Cross Reference | C - 6 |

| <i>C.4</i> | Timing                     | C - 7 |

| C.5        | CXC Backplanes             | C - 8 |

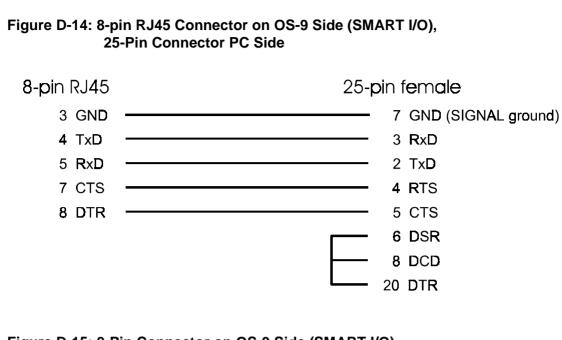

| D. OS- | 9 Cabling D - 3                                                    |

|--------|--------------------------------------------------------------------|

| D.1 OS | -9 System – Terminal D - 3                                         |

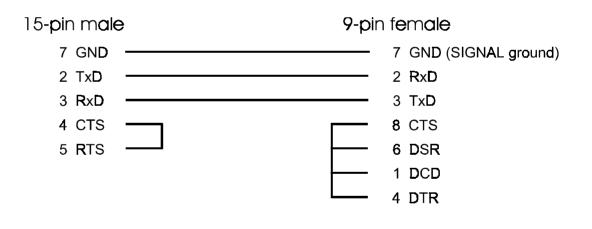

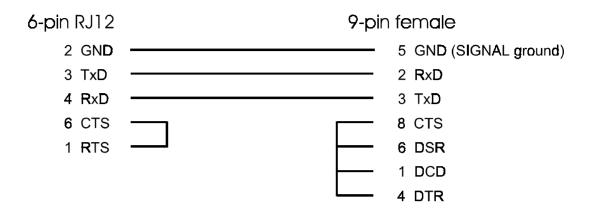

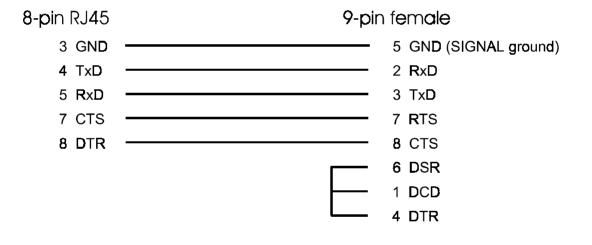

| D.1.1  | Software (XON/XOFF) or No Handshake D - 3                          |

| D.1.2  | Hardware Handshake (Set Terminal to CTS/DTR Handshake) D - 4       |

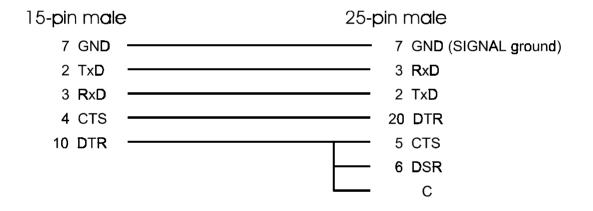

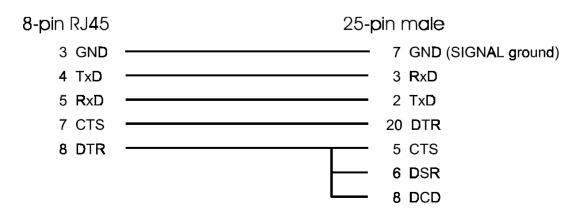

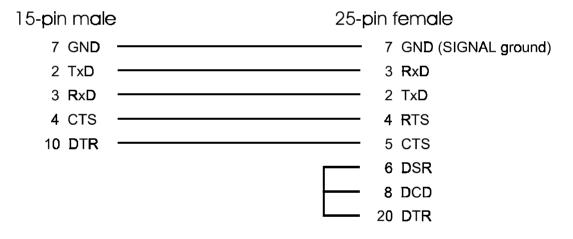

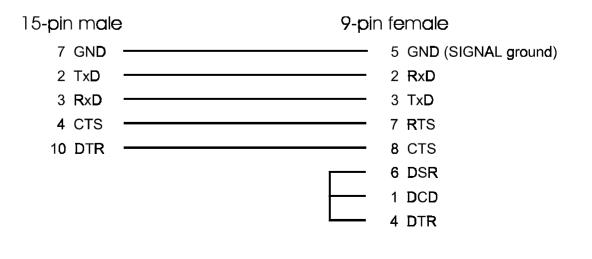

| D.2 OS | -9 System – PC D - 5                                               |

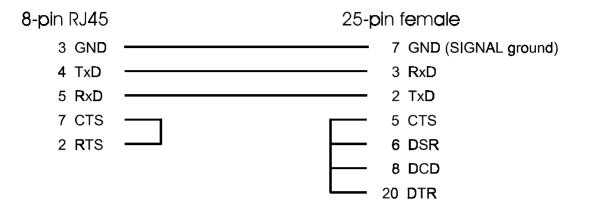

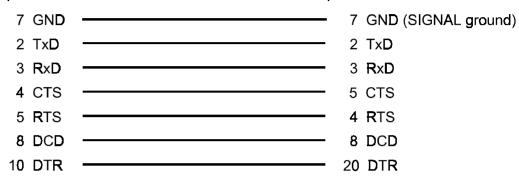

| D.2.1  | Software (XON/XOFF) or No Handshake D - 5                          |

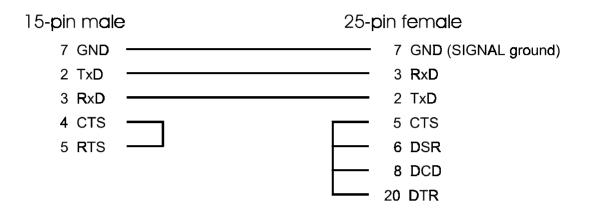

| D.2.2  | Hardware Handshake (Select RTS/CTS Handshake on the PC Side) D - 7 |

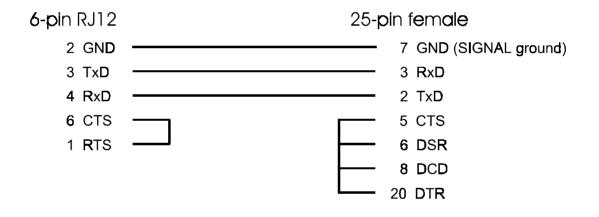

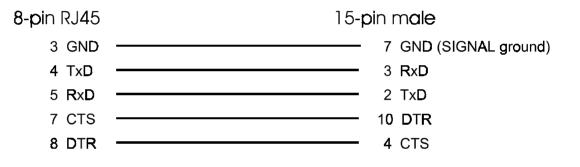

| D.3 OS | -9 System – Modem D - 9                                            |

| D.4 OS | -9 System – OS-9 System D - 10                                     |

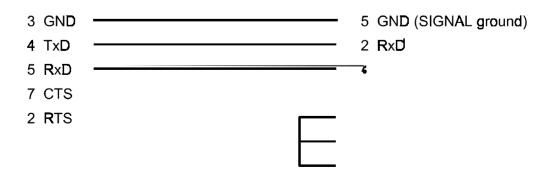

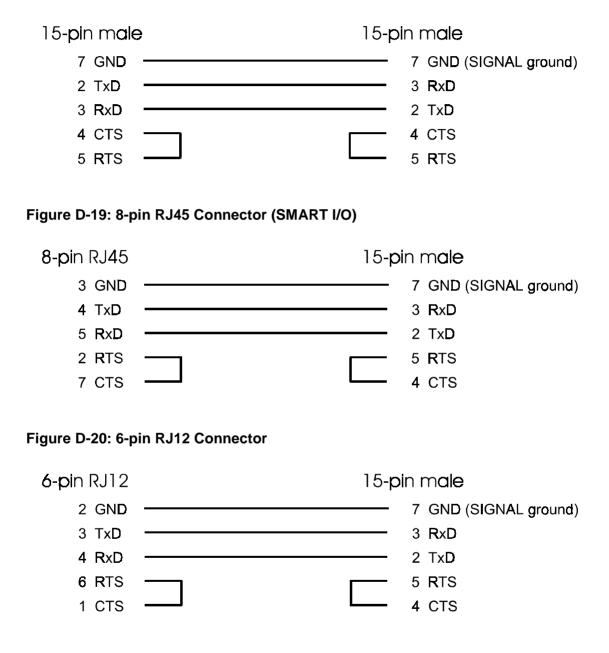

| D.4.1  | Software (XON/XOFF) or No Handshake D - 10                         |

| D.4.2  | Hardware Handshake D - 11                                          |

# Preface

This page was intentionally left blank.

# Preface

## **Proprietary Note**

This document contains information proprietary to *PEP Modular Computers*. It may not be copied or transmitted by any means, disclosed to others or stored in any retrieval system or media, without the prior written consent of *PEP Modular Computers GmbH* or one of its authorized agents.

The information contained in this document is, to the best of our knowledge, entirely correct. However, *PEP Modular Computers* cannot accept liability for any inaccuracies, or the consequences thereof, nor for any liability arising from the use or application of any circuit, product, or example shown in this document.

PEP Modular Computers reserve the right to change, modify, or improve this document or the product described herein, as seen fit by *PEP Modular Computers* without further notice.

#### Trademarks

*PEP Modular Computers*, the *PEP* logo and, if occurring in this manual, "CXM" are trade marks owned by *PEP Modular Computers GmbH*, Kaufbeuren (Germany). In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, proprietary to their respective owners.

#### **Explanation of Symbols**

#### CE Conformity

This symbol indicates that the product described in this manual is in compliance with all applied CE standards. Please refer also to the section "Applied Standards" in this manual.

#### Caution, Electric Shock!

This symbol and title warn of hazards due to electrical shocks (> 60V) when touching products or parts of them. Failure to observe the precautions indicated and/or prescribed by the law may endanger your life/health and/or result in damage to your material.

Please refer also to the section "High Voltage Safety Instructions" on the following page.

#### Warning, ESD Sensitive Device!

This symbol and title inform that electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

Please read also the section "Special Handling and Unpacking Instructions" on the following page.

#### Warning!

This symbol and title emphasize points which, if not fully understood and taken into consideration by the reader, may endanger your health and/or result in damage to your material.

#### Note...

This symbol and title emphasize aspects the reader should read through carefully for his or her own advantage.

#### PEP Advantage

This symbol and title emphasize advantages or positive aspects of a product and/or procedure.

### For Your Safety

Your new *PEP* product was developed and tested carefully to provide all features necessary to ensure the renown electrical safety requirements. It was also designed for a long fault-free life. However, the life expectancy of your product can be drastically reduced by improper treatment during unpacking and installation. Therefore, in the interests of your own safety and of the correct operation of your new *PEP* product, you are requested to conform with the following guidelines.

#### **High Voltage Safety Instructions**

#### Warning!

All operations on this device must be carried out by sufficiently skilled personnel only.

#### Caution, Electric Shock!

However, serious electrical shock hazards exist during all installation, repair and maintenance operations with this product. Therefore, always unplug the power cable to avoid exposure to hazardous voltage.

Before installing your new *PEP* product into a system always ensure that your mains power is switched off. This applies also to the installation of piggybacks.

#### **Special Handling and Unpacking Instructions**

#### ESD Sensitive Device!

Electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

- Do not handle this product out of its protective enclosure while it is not used for operational purposes, unless it is otherwise protected.

- Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where safe work stations are not guaranteed, it is important for the user to be electri-cally discharged before touching the product with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

- It is particularly important to observe standard anti-static precautions when changing piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC or memory back-up, ensure that the board is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or tracks on the board.

#### **General Instructions on Usage**

- In order to maintain *PEP's* product warranty, this product must not be altered or modified in any way. Changes or modifications to the device, which are not explicitly approved by *PEP Modular Computers* and described in this manual or received from *PEP* Technical Support as a special handling instruction, will void your warranty.

- This device should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This applies also to the operational temperature range of the specific board version, which must not be exceeded. If batteries are present, their temperature restrictions must be taken into account.

- In performing all necessary installation and application operations, please, follow only the instructions supplied by the present manual.

- Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the board please re-pack it as nearly as possible in the manner in which it was delivered.

- Special care is necessary when handling or unpacking the product. Please, consult the special handling and unpacking instruction on the following page of this manual.

### **Two Year Warranty**

*PEP Modular Computers* grants the original purchaser of *PEP* products a *TWO YEAR LIMITED HARDWARE WARRANTY* as described in the following. However, no other warranties that may be granted or implied by anyone on behalf of *PEP* are valid unless the consumer has the express written consent of *PEP Modular Computers*.

*PEP Modular Computers* warrants their own products, excluding software, to be free from manufacturing and material defects for a period of 24 consecutive months from the date of purchase. This warranty is not transferable nor extendible to cover any other users or long-term storage of the product. It does not cover products which have been modified, altered or repaired by any other party than *PEP Modular Computers* or their authorized agents. Furthermore, any product which has been, or is suspected of being damaged as a result of negligence, improper use, incorrect handling, servicing or maintenance, or which has been damaged as a result of excessive current/voltage or temperature, or which has had its serial number(s), any other markings or parts thereof altered, defaced or removed will also be excluded from this warranty.

If the customer's eligibility for warranty has not been voided, in the event of any claim, he may return the product at the earliest possible convenience to the original place of purchase, together with a copy of the original document of purchase, a full description of the application the product is used on and a description of the defect. Pack the product in such a way as to ensure safe transportation (see our safety instructions).

*PEP* provides for repair or replacement of any part, assembly or sub-assembly at their own discretion, or to refund the original cost of purchase, if appropriate. In the event of repair, refunding or replacement of any part, the ownership of the removed or replaced parts reverts to *PEP Modular Computers*, and the remaining part of the original guarantee, or any new guarantee to cover the repaired or replaced items, will be transferred to cover the new or repaired items. Any extensions to the original guarantee are considered gestures of goodwill, and will be defined in the "Repair Report" issued by *PEP* with the repaired or replaced item.

*PEP Modular Computers* will not accept liability for any further claims resulting directly or indirectly from any warranty claim, other than the above specified repair, replacement or refunding. In particular, all claims for damage to any system or process in which the product was employed, or any loss incurred as a result of the product not functioning at any given time, are excluded. The extent of *PEP Modular Computers* liability to the customer shall not exceed the original purchase price of the item for which the claim exists.

*PEP Modular Computers* issues no warranty or representation, either explicit or implicit, with respect to its products' reliability, fitness, quality, marketability or ability to fulfil any particular application or purpose. As a result, the products are sold "as is," and the responsibility to ensure their suitability for any given task remains that of the purchaser. In no event will *PEP* be liable for direct, indirect or consequential damages resulting from the use of our hardware or software products, or documentation, even if PEP were advised of the possibility of such claims prior to the purchase of the product or during any period since the date of its purchase.

Please remember that no *PEP Modular Computers* employee, dealer or agent is authorized to make any modification or addition to the above specified terms, either verbally or in any other form, written or electronically transmitted, without the company's consent.

This page was intentionally left blank.

Introduction

This page was intentionally left blank.

# 1. Introduction

#### **1.1 System Overview**

The *PEP Modular Computers* product described in this chapter operates with the VMEbus architecture. In addition, some products also support the CXC and/or Enhanced CXC (eCXC) local mezzanine interface standards which represent a streamlined variant of the VMEbus standard itself. Thus a wide range of I/O functions for industrial applications are supplied. Some of the major advantages of the VMEbus standard are:

- internationally accepted VITA standards (VMEbus, CXC, eCXC);

- broad range of available VMEbus solutions

- scalable processor performance

In addition, in combination with (e)CXC technology the VMEbus equipment offers the following advantages:

- lower costs and optimized reliability thanks to reduced design complexity;

- compact I/O sub-systems thanks to easier I/O wiring.

For detailled information concerning the VMEbus and (e)CXC standards, please consult the VMEbus and CXC Specifications which are available via the VMEbus International Trade Association (VITA): http://www.vita.com.

Many system-relevant features that are specific for VMEbus systems can be found in the ANSI/VITA VME64 Standard and in the VITA/*PEP* CXC MPI Specification which, despite its name, applies also to VMEbus MPI carriers.

The VME64 Standard includes the following information:

- VMEbus Specification

- Signal Lines, Bus Modules, Typical Operation

- Electrical Specifications

- Mechanical Specifications

The CXC MPI Specification includes the following information:

- Mechanical dimensions

- Electrical specifications

- Interface description

- ID Byte assignment

With reference to the (e)CXC aspects of mixed VMEbus+CXC systems please refer also to the *PEP* CXC Reference Manual.

## 1.2 Board Overview

#### 1.2.1 Board-Specific Information

The VSBC-32(E) is a 3U (Enhanced) CXC combined system and communications controller board that can operate in either a VMEbus or a mixed VMEbus+CXC environment. The board is based on the Motorola Quad Integrated Communications Controller "QUICC" MC68(EN)360. Therefore, it is particularly suitable for system control functions within applications with communications requirements. Depending on the controller chip used, there are two board variants with different CPU frequencies. The board's external interfacing consists of a twin RS232 interface connector, which can be extended by means of a variety of serial interface piggybacks and/or external serial interface modules. Other piggybacks provide DRAM/flash memory.

Some of the outstanding features of the product described in this manual are:

- VMEbus system and communications controller board

- Both VMEbus and eCXC connectivity

- Master/slave system controller functionality

- 32-bit Motorola MC68(EN)360 integrated CPU and communications controller

- 25Hz or 33Hz CPU frequency

- CPU on-chip background debugging

- 1, 4, 16, 32 or 64 MB DRAM

- 0, 0.5, 1, 2 or 4 MB flash memory

- 256kB or 1 MB SRAM

- 2kbit serial EEPROM

- 256kB or 1MB DIP (flash) EPROM

- Real-time clock (backed-up)

- Six different communication standards possible:

- Serial I/O (RS232, RS485; RS422 on request)

- Ethernet (10Base2, 10Base5 or 10BaseT Ethernet)

- Up to six frontpanel serial interface connectors

- Compatibility with external serial interface module CXM-SIO3

- Reset and Abort control (frontpanel buttons)

- Halt, watchdog and general-purpose status indicators (frontpanel LED's)

- OS-9 and VxWorks<sup>®</sup> drivers

#### 1.2.2 Board Variants

Two basic variants of the VSBC-32(E) with different processors are available. Depending on the controller chip used and the SRAM size, there are four variants of the VSBC-32(E) system and serial communications controller board. The distinctive features of the variants are listed in the following

- Ethernet capability

- CPU frequency

- SRAM size

The following basic board variants are available:

- VSBC-32: MC68360 processor, no Ethernet control capability.

- VSBC-32E:MC68EN360 processor, Ethernet control capability.

The MC68EN360 processor is also available with two different clock rates:

- 25MHz

- 33MHz (this variant is again supplied with either 256kB or 1MB SRAM).

The below described frontend connectivity and interface expandibility are common to all board variants.

#### 1.2.3 Board Connectivity and Interface Expandibility

The VSBC-32(E) mainboard is provided with the following standard connectors:

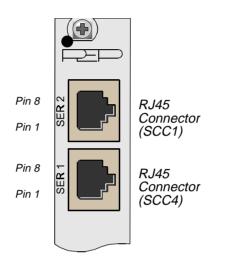

- Non-optoisolated RS232 serial interface (two RJ45 connectors, on frontpanel)

- One set of piggyback interface connectors for serial interface (SI) piggybacks (three 7-pin row male connectors)

- One set of memory piggyback interface connectors (two 50-pin row female connectors)

- Two sets of (flash) EPROM DIP sockets (two 32-pin row female sockets)

- Background debug mode (BDM) interface (one 12-pin row male connector)

- VMEbus backplane interface

(one 96-pin DIN 41612, style C male connector)

- Enhanced CXC mezzanine interface (one 96-pin DIN 41612, style C male connector)

In addition, the mainboard external interfacing is usually integrated by one of the following piggyback-mounted frontpanel interface options (serial interface piggybacks). The kinds of piggyback that can be used depend on the mainboard variant.

| Piggyback    | Description                                                           | Board Variant        |

|--------------|-----------------------------------------------------------------------|----------------------|

| SI-PB232     | Non-optoisolated RS232 serial interface (two RJ45 connectors)         | VSBC-32,<br>VSBC-32E |

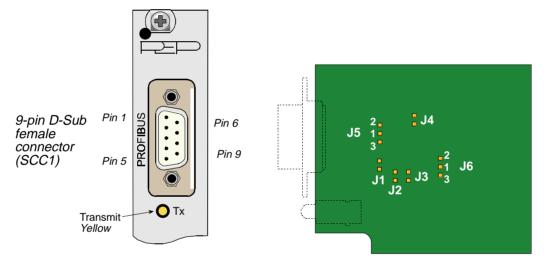

| SI-PB485-ISO | Optoisolated RS485 serial interface (one 9-pin female DSUB connector) | VSBC-32,<br>VSBC-32E |

| SI-10B2      | 10Base2 Ethernet interface (one RG58 coaxial connector)               | VSBC-32E             |

| SI-10B2      | 10Base2 Ethernet interface (one RG58 coaxial connector)               | VSBC-32E             |

| SI-10BT      | 10BaseT Ethernet interface (one RJ45 connector)                       | VSBC-32E             |

#### Table 1-1: Serial Interface Piggybacks

Applications requiring further communication interfaces may be upgraded by means of an external CXM-SIO3 serial interface module which provides the following interface extension possibilities:

- RS232 serial interface connectors (non-optoisolated)

- Serial interface piggyback ports

- Serial communications piggyback port

Maximum one CXM-SIO3 module can be controlled by a VSBC-32(E) board. The CXM-SIO3 module provides access to internal communication signals of the base board that are transferred to the module via the CXC bus.

For a detailled list and description of the frontpanel interface and serial interface/communication piggybacks please refer to the "Serial Interface Piggybacks" appendix of this manual as well as to the CXM-SIO3 user's manual and its "Serial Communications Piggybacks" appendix respectively.

#### 1.2.4 Memory Piggybacks

The VSBC-32(E) mainboard is not provided with any on-board DRAM/flash. These are provided by special memory piggybacks (DM60x). By means of these piggybacks the following memory configurations are possible:

- ≤64MB of DRAM

- ≤4MB of flash/EPROM

For a detailled description of the memory piggybacks please refer to the "Memory Piggybacks" appendix of this manual.

#### 1.2.5 System-Relevant Information

#### System Configuration

Up to twenty-one VSBC-32(E) boards can be installed in a VMEbus 3U rack. Please refer to the description of the VMEbus backplane connector in the Functional Description chapter of this manual. If used as a system controller, the board should be always installed in the system slot.

If a CXM-SIO3 or a CXM-SCSI module is used in combination with the VSBC-32(E), the module can be "sandwiched" with the controller, Communication between the controller and the I/O module being acchieved via the VSBC-32(E)'s on-board CXC connector.

#### Master/Slave Functionality

The VSBC-32(E) is a combined system and communications controller board provided with both a VMEbus backplane interface which can operate both as a VMEbus master and slave simultaneously. Thanks to this feature all twenty-one VSBC-32(E) boards possible in a VMEbus system can operate as VMEbus masters while at the same time sixteen of them can act as VMEbus slaves. The VSBC-32(E) VMEbus master/slave (or neither) operation is a function of the application software.

#### Bootstrap Loader

Via the VSBC-32(E) frontend serial interface connectors the flash memory of the board's memory piggyback can be re-programmed by means of the Bootstrap Loader which is delivered already installed in the DM60x memory piggybacks. This standalone software has the capability of loading flash memory from Motorola S-records or from any absolute address. If the downloaded image does not work properly, the Bootstrap

Loader can be re-entered, the memory contents analyzed and a further programming cycle initiated.

#### Warning!

To avoid damaging of your Bootstrap Loader and, consequently, leaving your board unusable, please read the separate Bootstrap Loader manual before re-setting the flash contents of your VSBC-32 board.

#### **Operating Systems**

The VSBC-32(E) can operate under the following operating systems:

- OS-9

- VxWorks<sup>®</sup>

Drivers are available for both operating systems. Porting to other operating systems on request.

## 1.3 Board Diagrams

#### 1.3.1 System-Level Functional Block Diagram

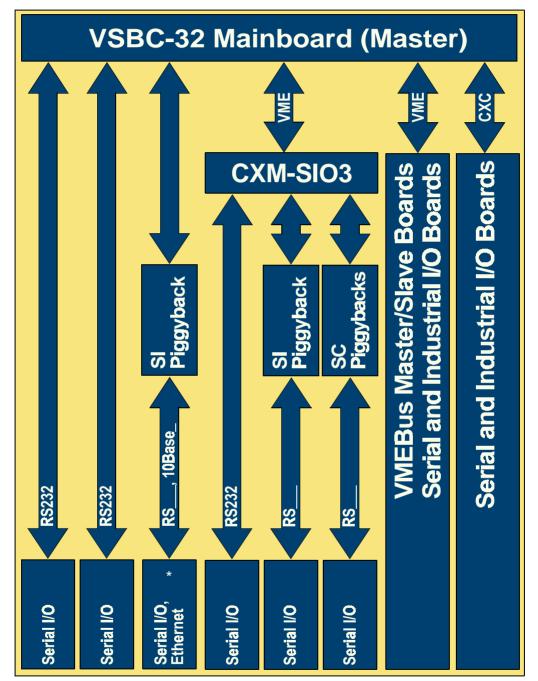

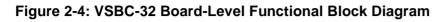

Figure 1-1: VSBC-32(E) System-Level Functional Block Diagram

#### Legend:

RS\_\_[I]: 10Base\_: RS232 non-optoisolated or RS485 optoisolated 10Base2 or 10Base5 or 10BaseT Ethernet

\* Serial I/O or Ethernet (Ethernet with VSBC-32E only)

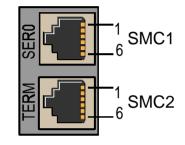

#### 1.3.2 **Frontpanels**

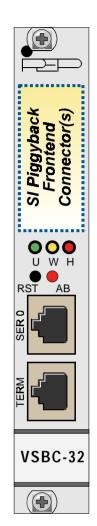

Figure 1-2: VSBC-32(E) Frontpanel

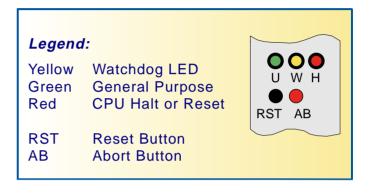

#### LED's:

- Green ("U"): General purpose

- Yellow ("W"):

- Watchdog • Red ("H"): Halt

#### **Pushbuttons:**

- RST (left): Reset

- AB (right): Abort

#### SI Piggyback Frontend Connector(s):

The additional frontend connector(s) depend(s) on the type of serial interface piggyback installed in combination with the VSBC-32(E) mainboard. For any details, please refer to the "Serial Interface Piggybacks" appendix in this manual.

## VSBC-32

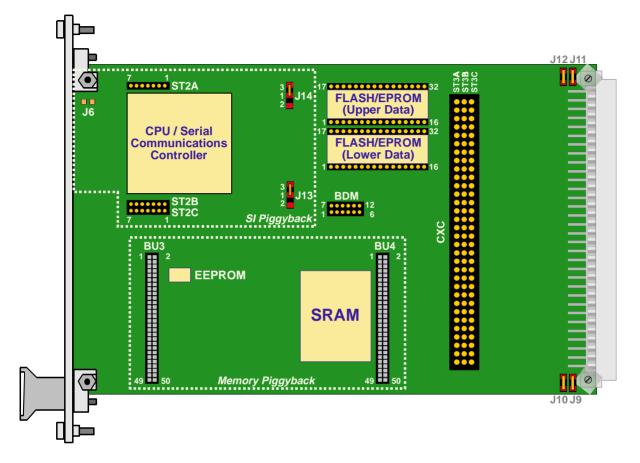

#### 1.3.3 Board Layouts

#### Figure 1-3: VSBC-32(E) Board Diagram (front)]

#### FLASH/EPROM:

| Upper Data: | D8-D15, even Byte addresses |

|-------------|-----------------------------|

| Lower Data: | D0-D7, odd Byte addresses   |

| BDM:        | Background Debug Mode.      |

#### Warning!

Solder jumpers are factory-set. To avoid possible damage to your equiment, please do not alter them.

## **1.4 Technical Specifications**

#### Table 1-2: VSBC-32(E) Technical Specification (Sheet 1 of 3)

| VSBC-32(E)                                       | Specification                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Board Variants                                   | <ul><li>VSBC-32:</li><li>VSBC-32E:</li></ul>                                                                                                                                                                                                                                                                                                                                                   | MC68360 processor,<br>MC68EN360 processor                                                                                                                                                                                                        |  |

| Combined CPU/Serial<br>Communications Controller | <ul><li>MC68360:</li><li>MC68EN360:</li></ul>                                                                                                                                                                                                                                                                                                                                                  | 25 MHz, no Ethernet capability<br>25MHz or 33 MHz, Ethernet capability                                                                                                                                                                           |  |

|                                                  | CPU performance:<br>Serial I/O perform.:                                                                                                                                                                                                                                                                                                                                                       | Equivalent to Motorola CPU32<br>RISC, 14 dedicated DMA channels                                                                                                                                                                                  |  |

| On-Board Memory                                  | <ul> <li>SRAM</li> <li>EEPROM</li> <li>Flash/EPROM</li> </ul>                                                                                                                                                                                                                                                                                                                                  | 256kB or 1MB (dual-ported,<br>backed-up by means of Gold-Caps)<br><u>Note:</u> 1MB with VSBC-32E only.<br>2 kbit (serial); 1 kbit available<br>for applications<br>256kB or 1MB DIP EPROM/flash,<br>16-bit access<br>Minimum access time - 120ns |  |

| Memory on Piggybacks                             | <ul><li>DRAM</li><li>Flash</li></ul>                                                                                                                                                                                                                                                                                                                                                           | 1, 4, 16 or 32 MB, 32-bit access<br>0, 0.5, 1, 2 or 4 MB, 32-bit access                                                                                                                                                                          |  |

| VMEbus Master/Slave<br>Functionality             | <ul><li>Master</li><li>Slave</li></ul>                                                                                                                                                                                                                                                                                                                                                         | A24:D16/D8, arbitration, AM codes<br>A24:D16, dual-port RAM, mailbox IRQ                                                                                                                                                                         |  |

| Interrupt Control                                | <ul> <li>7-level CXC/VME IRQ handler, maskable via CXC/VME interrupt mask register; system vectors:</li> <li>ACFAIL* (via VME)Level 7 autovectored</li> <li>Abort Level 7 autovectored</li> <li>Tick Level 6 autovectored</li> <li>Mailbox IRQ Level 5 autovectored, maskable</li> <li>SYSFAIL* Level 3 autovectored</li> <li>16 on-board interrupters; levels/vectors programmable</li> </ul> |                                                                                                                                                                                                                                                  |  |

| Programmable Timers                              | <ul> <li>Tick: Periodic-interrupt timer</li> <li>Watchdog: 512ms time-out for reset</li> <li>On-board bus error:8µ s</li> <li>General-purpose: 4*16 bit or 2*32 bit</li> </ul>                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                  |  |

| Special Functions                                | <ul> <li>Real-time clock (backed-up):</li> <li>Date (year, month, week, day)</li> <li>Time (hour, minute, second)</li> <li>2kbit serial EEPROM:</li> <li>1kbit for board specific data (serial number, IP address etc.)</li> <li>1kbit for application purposes</li> <li>DMA: 2 additional independent channels<br/>(transfers between DRAM, FLASH, VME and CXC)</li> </ul>                    |                                                                                                                                                                                                                                                  |  |

| VSBC-32(E)              | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Communication Standards | <ul> <li>Serial I/O (RS232, RS422, RS485)</li> <li>Ethernet (VSBC-32E only)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Mainboard Connectivity  | <ul> <li>Non-optoisolated RS232 serial interface<br/>(two RJ12 connectors, on frontpanel)</li> <li>One set of piggyback interface connectors for serial inter-<br/>face (SI) piggybacks (two 13-pin row fe/male connectors)</li> <li>One set of memory piggyback interface connectors<br/>(two 50-pin row fe/male connectors)</li> <li>Background debug mode (BDM) interface<br/>(one 12-pin row male connector)</li> <li>VMEbus backplane interface<br/>(one 96-pin DIN 41612, style C male connector)</li> <li>Enhanced CXC mezzanine interface<br/>(one 96-pin DIN 41612, style C male connector)</li> </ul>                                            |  |  |

| Interface Expandibility | Serial interface piggybacks:         • SI-PB232:       non-optoisolated RS232 serial interface (two RJ45 connectors)         • SI-PB485-ISO:       optoisolated RS485 serial interface (two RJ45 connectors)         • SI-10B2:       10Base2 Ethernet interface (one RG58 coaxial connector)         • SI-10B5:       10Base5 Ethernet interface (one 15-pin DSUB female connector)         • SI-10BT:       10BaseT Ethernet interface (one RJ45 connector)         • SI-10BT:       10BaseT Ethernet interface (one RJ45 connector)         • SI-10BT:       10BaseT Ethernet interface (one RJ45 connector)         • CXM-SIO3       Up to one module. |  |  |

| Front-End Functions     | Pushbuttons:         • Reset button         • Abort button         LED's:         • Red:       Halt         • Yellow       Watchdog         • Green       General purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

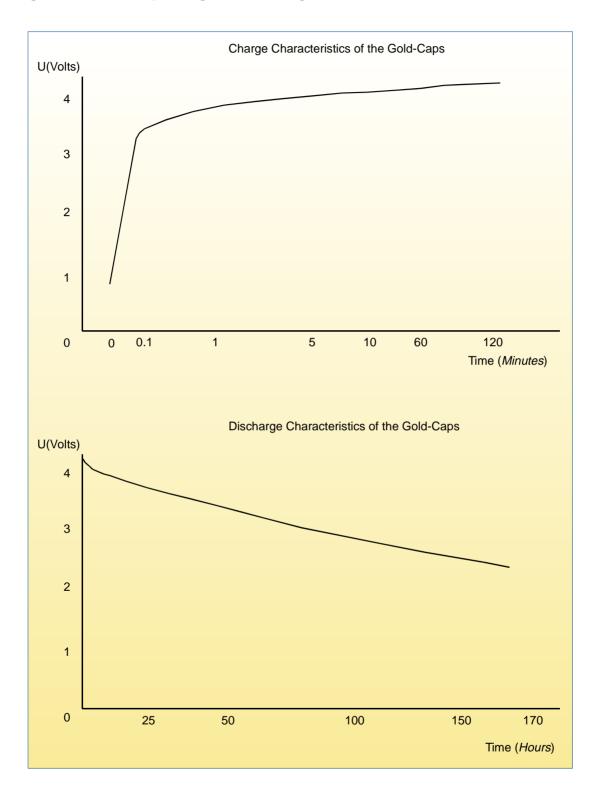

| Data Retention          | Short-term backup (RTC and SRAM):<br>Via on-board gold-cap. Typ. 2μ A/3V -> 150 hours<br>Long-term backup:<br>Via VME 5V stand-by line; automatic switching between 5V<br>stand-by and internal gold-cap. Typ. 30μ A/3V                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Power Supply            | Typically:5VWith SI-PB5B:12V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

#### Table 1-2: VSBC-32(E) Technical Specification (Sheet 2 of 3)

| VSBC-32(E)         | Specification                                                                                    |  |  |

|--------------------|--------------------------------------------------------------------------------------------------|--|--|

| Power Consumption  | <ul> <li>VSBC-32: typ. 3.0W</li> <li>VSBC-32E: typ. 3.5W</li> </ul>                              |  |  |

| Temperature Ranges | Operation:<br>0°C to 70°C (standard)<br>-40°C to +85°C (extended)<br>Storage:<br>-55°C to +125°C |  |  |

| Humidity           | 095%, non-condensing                                                                             |  |  |

| Dimensions         | 4HP/3U Eurocard (100mm x 160mm)                                                                  |  |  |

| Weight             | Mainboard:130gSerial interface piggyback:2030gMemory piggyback:30g                               |  |  |

#### 1.5 Applied Standards

#### 1.5.1 CE Compliance

The *PEP Modular Computers'* VMEbus and (e)CXC systems comply with the requirements of the following CE-relevant standards:

| • | Emission          | EN50081-1 |

|---|-------------------|-----------|

| • | Immission         | EN50082-2 |

| • | Electrical Safety | EN60950   |

#### 1.5.2 Mechanical Compliance

Mechanical Dimensions IEEE 1101.10

#### 1.5.3 Environmental Tests

| • | Vibration       | IEC68-2-6  |

|---|-----------------|------------|

| • | Permanent Shock | IEC68-2-29 |

| • | Single Shock    | IEC68-2-27 |

### **1.6 Related Publications**

#### 1.6.1 VMEbus/CXC Systems/Boards

- ANSI/VITA: VME64 Draft Specification 1-1994, Rev. 1.9

- VITA: CXC Specification, Rev. 2.0

- PEP Modular Computers CXC MPI Draft Specification, Rev. 3.1 (ID 12190)

- PEP Modular Computers CXC Reference Manual, ID 05263

- PEP Modular Computers CXM-SIO3 Manual (ID 14411)

- PEP Modular Computers CXM-SCCI Manual (ID 03545)

#### 1.6.2 Manufacturers' Component Documentation

- Motorola: MC68EN360 Quad Integrated Communications Controller User's Manual

- EM Microelectronic:V3021 1-Bit Real-Time Clock Datasheet

- XICOR:X25C02 SPI Serial EEPROM Datasheet

This page was intentionally left blank.

Functional Description

This page was intentionally left blank.

# 2. Functional Description

### 2.1 General Information

The VSBC-32(E) is a 3U VMEbus combined system and communications controller board based on the Motorola Quad Integrated Communications Controller "QUICC" MC68(EN)360. Depending on the controller chip used and the SRAM size, there are four board variants with different characteristics. The following table provides an overview of the various VSBC-32(E) board variants.

Table 1-1: VSBC-32(E) Board Variants

| Board Name | Processor | Ethernet<br>Capability | Processor<br>Frequency | SRAM Size |

|------------|-----------|------------------------|------------------------|-----------|

| VSBC-32    | MC68360   | —                      | 25MHz                  | 256kB     |

|            | MC68EN360 | +                      | 25MHz                  | 256kB     |

| VSBC-32E   |           | +                      | 33MHz                  | 256kB     |

|            |           | +                      | 33MHz                  | 1MB       |

Being the MC68(EN)360 a CPU and serial communications controller, it is particularly suitable for system control functions within applications with communications requirements such as LAN, WAN or fieldbusses (CAN, LON, PROFIBUS).

In fact, both the VSBC-32 and the VSBC-32E allow for a wide range of serial interfaces based on the MC68(EN)360 controller which is able to handle up to six serial communications channels. The channels can be configured in the following way:

- Two service / debug interface connectors (SMC interface, RxD/TxD, RS232 only)

- Four full modem interface connectors / multiprotocol channels (SCC interfaces).

Thus, the VSBC-32(E) mainboard comes complete with two non-optoisolated RS232 external interfaces which are located on the lower half of the front panel. However, the external serial interfacing can be extended by means of a variety of serial interface (SI) piggybacks and/or a CXM-SIO3 type external serial interface module. This external module can be either "sandwiched" with the controller or placed to the right of the VSBC-32(E). In the first case, communication between the controller and the I/O module is acchieved via the VSBC-32(E)'s on-board CXC connector, in the second case via the VMEbus.

As the CXM-SIO3 can be used again as a carrier for various serial interface (SI) and serial communications (SC) piggybacks, the VSBC-32/CXM-SIO3 tandem represents a really powerful and versatile system control and serial communications control set.

Together with the two service/debug interfaces, a maximum of three (four with the serial interface piggyback fitted) completely configured serial interfaces are available for the base board. Three (two with serial interface piggyback fitted) serial interfaces may be configured via the VMEbus where three of the four full modem Interfaces are routed.

The VSBC-32(E) allows also a significant variety of memory configurations, mainly DRAM and flash memory located on special memory piggybacks, add-on flash/EPROM on DIP sockets, battery backed-up SRAM and EEPROM.

#### 2.2 Specifics

#### 2.2.1 System Control Functionality

Under the aspect of system control the on-chip 32-bit CPU core of the Motorola MC68(EN)360 provides system integration at different processor frequencies. The processor core acts essentially as a Motorola CPU32 microprocessor operating at 25MHz or 33MHz without cache memory. In addition, the MC68(EN)360 offers background debugging via the on-chip "Background Debug Mode" which allows direct communication with the CPU.

To act as a system controller, the VSBC-32(E) is provided with arbiter, system clock driver, power monitor with system reset driver, IACK daisy chain driver and 7-level VMEbus interrupt controller.

Arbitration is single-level FAIR (compare VME64 Specification Rule 3.14/Observation 3.17). If the VSBC-32(E) is used as a system controller and consequently placed in the VMEbus backplane's system slot, a special detection function provided by the board makes any "slot 1" jumper setting superfluous. The VSBC-32(E) also provides a bus monitor for the VMEbus.

#### Interrupt Control

The interrupt control logic of the MC68(EN)360 processes internal interrupt requests alongside with external autovectored interrupt requests and a "mailbox" interrupt request from the VMEbus control/status register. The interrupt control logic is built up using the processor's internal interrupt control and an external IRQ7 interrupt handler.

Internal requests are related to all interrupt requests caused by the controller sources, including the processor's system integration functions (watchdog timer, periodic interrupt timer) and the communications processor module (RISC controller, timers, DMA's, SCC's etc.).

In order to avoid conflicts regarding the different interrupt levels, it is recommended to use IRQ level 4 for the MC68(EN)360 CPU internal requests and IRQ level 6 for the MC68(EN)360 serial controller internal requests.

In addition, external interrupt sources can generate autovectored interrupts and an external VMEbus master may require an interrupt by setting a "mailbox" IRQ in the VMEbus control/status register.

For any detailled information as well as a complete list of the Motorola<sup>®</sup> MC68(EN)360 controller signals please refer to the relating Data Sheet.

| Source          | Interrupt Source      | Interrupt Type          |

|-----------------|-----------------------|-------------------------|

| ABORT / ACFAIL  | MC68(EN)360, pin IRQ7 | Autovector 7            |

| Reserved        | MC68(EN)360, pin IRQ6 | Autovector 6            |

| Mailbox IRQ     | MC68(EN)360, pin IRQ5 | Autovector 5            |

| Reserved        | MC68(EN)360, pin IRQ4 | Autovector 4            |

| SYSFAIL         | MC68(EN)360, pin IRQ3 | Autovector 3            |

| Reserved        | MC68(EN)360, pin IRQ2 | Autovector 2            |

| Reserved        | MC68(EN)360, pin IRQ1 | Autovector 1            |

| Mailbox Pending | Bit P_IRQ5            | Control/status register |

#### 2.2.2 Memory Configurations

The VSBC-32(E) allows a significant variety of memory configurations. The special DRAM/flash piggybacks (DM60x), for instance, allows the user to take advantage of the on-board programming facility to produce low cost upgrades by simply overwriting existing stored data. This memory can be configured with different memory options allowing remarkable flexibility when customizing memory requirements for real-time applications.

The DM60x piggybacks provide between 1MB and 64MB of DRAM with 32-bit access and up to 4MB of +5V flash memory. In addition, a set of DIP sockets located on the VSBC-32(E) mainboard allows the installation of an additional 1MB of flash/EPROM. Both memory devices can be used for bootstrapping. The selection of the boot memory is achieved by hardware jumpering.

#### Note...

Physically the DM60x piggybacks provide up to 64MB of DRAM. However, the IUC-32(E) mainboard envisages addressing for up to two memory banks of 64MB each.

Exchange and retention of system relevant data from the VMEbus to the CPU/DMA and viceversa is provided by means of 256kB or 1MB of a 16-bit wide dual-ported SRAM which is backed-up using Gold Caps. Both the VMEbus users and the on-board CPU have access to the SRAM memory.

#### Note...

The upper 8kB of dual-ported SRAM are accessed by the VMEbus, the lower 8kB are reserved for mailbox interrupts.

Configuration data are stored in a 2kbit EEPROM. 1kbit is used for factory-specific configuration purposes, and 1kbit is available for application-specific configuration data. A schematic overview of all possible memory configurations is given in the figure on the next page.

#### 2.2.3 DMA Channels

Two independent channels are provided by the MC68(EN)360 controller chip and can be used by applications requiring data transfer between VMEbus modules (as well as CXC modules, if present), DRAM, flash memory and dual-ported SRAM.

Memory-to-memory transfers with the DMA's of the MC68(EN)360 are possible with any combination of on-board and VMEbus addresses.

#### 2.2.4 Serial Communications Control

Under the aspect of serial communications control, a major advantage of the MC68(EN)360 serial communications controller core SIM60 is its compatibility with all important communication standards. A detailled description of all control functions is provided on the following pages alongside with a comprehensive list of the possible serial interface piggybacks and their connectors.

For the mainboard interface connector pinouts refer also to the "Board Interfaces" section of this chapter. For a description and pinouts of the connectors of the serial interface/communication piggybacks as well as of the CXM-SIO3 frontpanel interface connectors please refer instead to the "SI Piggybacks" appendix of this manual as well as to the CXM-SIO3 user's manual and its "Serial Communications Piggybacks" appendix respectively.

#### **Communication Standards and Protocols**

Six communication standards are available on the VSBC-32(E):

- Serial I/O (RS232, RS485; RS422)

- Ethernet (10Base2, 10Base5, 10BaseT)

Serial communications using the RS232 standard are available on the VSBC-32(E) mainboard frontpanel as well as on a dedicated piggyback to be connected to its SI Interface. In addition, RS232 communication is possible via a CXM-SIO3 external serial interface module. Communications using the PROFIBUS protocol are supported by an optoisolated, half-duplex RS485 serial I/O interface implemented on a dedicated piggy-back to be connected to the SI Interface of either the VSBC-32(E) or the external serial interface module. RS422 is not commonly available on the VSBC-32(E) but can be supplied by *PEP Modular Computers* on special request.

The MC68(EN)360 processor is specified to support also a full set of IEEE 802.3/Ethernet CSMA/CD media access control and channel interface functions. Since the controller requires an external interface adapter and transceiver function, the Ethernet interface can be adapted to all standard Ethernet functions, such as 10BaseT, 10Base5 and 10Base2 via a piggyback connected to the SI Interface on the VSBC-32(E).

#### Note...

The CXC bus does not support a 12V power supply. Therefore, the 10Base5 Ethernet piggyback SI-10B5 cannot be used on the IUC-32(E) controller board.

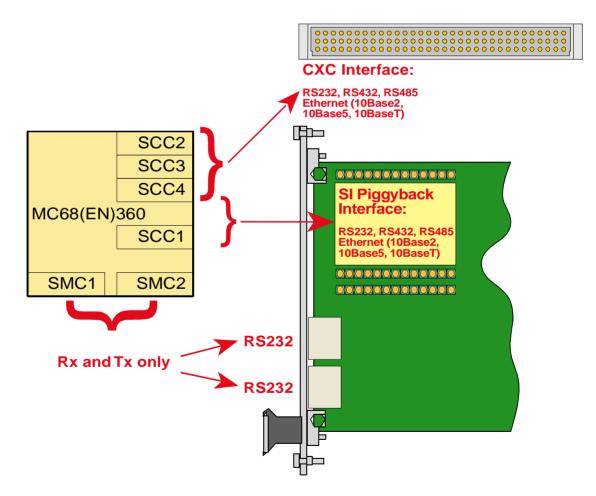

#### Serial I/O Channelling

The VSBC-32(E) mainboard is provided with TxD and RxD signals by the controller's SMC1 and SMC2 channels and supply RS232 interface software handshake (XON/ XOFF) capability. They are configured as service/debug connectors by default.

All full modem interfaces located on the piggybacks and/or CXM-SIO3 external serial interface module supply RxD, TxD, RTS, CTS, CD, DTR and RCLK/TCLK. Two of the full modem interfaces can be configured on the piggyback interface with a variety of

serial interface (SI) piggybacks (RS232, RS485, Ethernet). The SCC1 channel of the MC68(EN)360 provides the interface to the serial interface (SI) piggyback installed on the VSBC-32(E). All other channels of the controller (SCC2, SCC3 and SCC4) are ported to the CXC interface except for the SI-PB232 piggyback which has on-board additional control provided by the SCC4 channel through the piggyback interface for serial interface piggybacks.

Thanks to the fact that three out of four SCC channels are routed to the CXC interface connector, also an CXM-SIO3 external serial interface module can be installed in the system, which therefore becomes a sort of "privileged" serial I/O extension of the VSBC-32(E) board itself. In addition to two non-optoisolated RS232 serial interface connectors the external serial interface module supports again a serial interface piggyback and up to three serial communications piggybacks with the relating interfacing options. Maximum one CXM-SIO3 module can be controlled by an VSBC-32(E) board.

#### Figure 2-2: MC68(EN)360 Serial Communication Channeling

#### Note...

The serial channel SCC4 is routed to both the piggyback interface for serial interface piggybacks and the CXC and can be used by either one or the other, not both at the same time. Depending on whether the piggyback interface for serial interface (SI) piggybacks is configured as an Ethernet port (board versions with Ethernet piggyback) or not, the serial interfaces channels of the VSBC-32(E) can assume the functions described in the following figure.

#### Figure 2-3: VSBC-32(E) Serial Interface Channel Configurations

| Port            | Serial Communication<br>Channel | Interface Location                                                                |  |

|-----------------|---------------------------------|-----------------------------------------------------------------------------------|--|

| Service/Debug 1 | SMC1                            | Mainboard, upper RJ12                                                             |  |

| Service/Debug 2 | SMC2                            | Mainboard, Iower RJ12                                                             |  |

| Ethernet        | SCC1                            | Mainboard, serial interface piggyback                                             |  |

| Full MODEM 1    | 3001                            | Maniboard, Seriar Interface piggyback                                             |  |

| Full MODEM 2    | SCC2                            | External serial interface module                                                  |  |

| Full MODEM 3    | SCC3                            | External serial interface module                                                  |  |

|                 |                                 | External serial interface module <sup>1</sup>                                     |  |

| Full MODEM 4    | SCC4                            | Mainboard or<br>Serial interface piggyback or<br>External serial interface module |  |

Legend:

Board versions with Ethernet port Board versions without Ethernet port Independent of Ethernet configuration

<sup>1</sup> SCC4 is not used by any of the Ethernet piggybacks. With these piggybacks, SCC4 can be used on the CXC bus.

### 2.3 Functional Block Diagram

### 2.4 Board Interfaces

The following section provides a description of the mainboard interface connector pinouts. For a detailled list and description of the connectors of the serial interface/communication piggybacks and of the frontpanel interface connectors please refer to the "SI Piggybacks" appendix of this manual as well as to the CXM-SIO3 user's manual and its "Serial Communications Piggybacks" appendix respectively.

#### 2.4.1 Serial I/O Interfaces

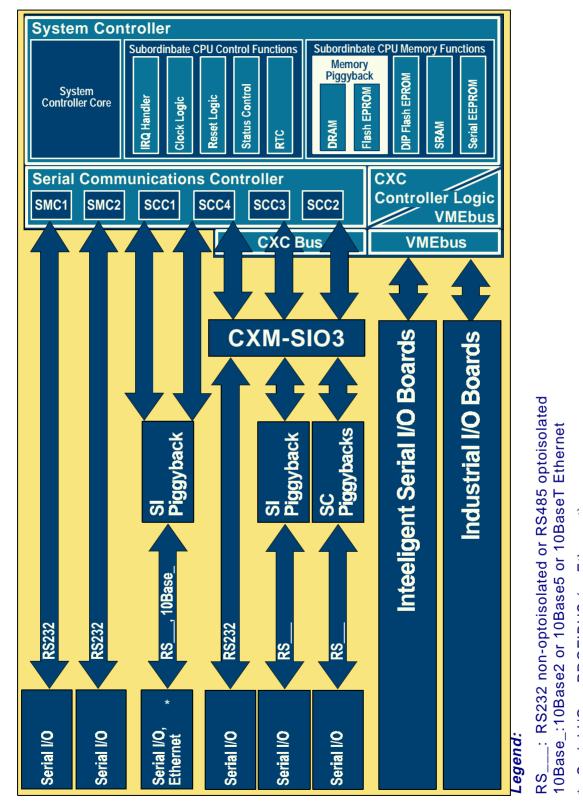

The mainboard RJ12 RS232 frontpanel connectors BU7 and BU8 of the VSBC-32(E) are provided with TxD and RxD signals by the controller's SMC1 and SMC2 channels and supply RS232 interface software handshake (XON/XOFF) capability. They are configured as service/debug connectors by default.

The pinouts of the RJ12 connectors are shown in the following table.

#### Figure 2-5: Orientation of the VSBC-32(E) Mainboard Serial Interfaces

| Pin | Pinouts |

|-----|---------|

| 1   | N/C     |

| 2   | GND     |

| 3   | TxD     |

| 4   | RxD     |

| 5   | N/C     |

| 6   | N/C     |

#### Table 2-3: Pinouts of the Mainboard Serial Interface Connectors BU7/BU8

N/C = Not connected.

#### 2.4.2 Piggyback Interface Connectors for Serial Interface Piggybacks

The VSBC-32(E) is equipped with a set of piggyback interface connectors for serial interface (SI) piggybacks (three 7-pin row male connectors). The pinout of these piggyback interface connectors includes all signals for serial I/O (RS232), PROFIBUS (RS485) and Ethernet (10BaseT, 10Base5, 10Base2) communication.

#### Note...

Although physically all piggybacks fit on bott basic board variants (IUC-32 and IUC-32E), the MN68360 processor of the IUC-32 variant does not support Ethernet communication. Therefore, Ethernet piggybacks should be used only on the IUC-32E board variants.

For a detailled description of the pinouts of these piggyback interface connectors please refer to the VITA/*PEP Modular Computers* CXC MPI Specification.

#### 2.4.3 Memory Piggyback Interface Connectors

The VSBC-32(E) is equipped with a set of memory piggyback interface connectors (two 50-pin row female connectors). The pinout of these piggyback interface connectors includes all signals for the connection of up to 128MB of DRAM and up to 4 MB of flash EPROM.

For a detailled description of the pinouts of these piggyback interface connectors please refer to the VITA/*PEP Modular Computers* CXC MPI Specification.

#### 2.4.4 EPROM DIP Sockets

The VSBC-32(E) is equipped with two sets of (flash) EPROM DIP sockets (two 32-pin row female sockets). The pinout of these DIP sockets includes all signals for the connection of up to 1MB of SRAM.

#### 2.4.5 Background Debug Mode Interface Connector

The VSBC-32(E) is equipped with a background debug mode (BDM) interface connector (one 12-pin row male connector). This connector allows an external debugger to be interfaced to the MC68(EN)360 for controlling purposes. The interface connector is specified by Motorola.

The pinouts of the BDM interface connector are shown in the following table. For any further details, please refer to the Motorola MC68(EN)360 User's Manual.

| Pin | Signal  | Pin | Signal        |

|-----|---------|-----|---------------|

| 1   | GND     | 2   | CLKO1         |

| 3   | DS*     | 4   | BERR*         |

| 5   | GND     | 6   | BKPT* / DSCLK |

| 7   | GND     | 8   | FREEZE        |

| 9   | RESETH* | 10  | IFETCH / DSI  |

| 11  | VCC     | 12  | IPIPE0 / DSO  |

#### Table 2-4: BDM Interface Connector Pinouts

#### 2.4.6 VMEbus Backplane Interface

The VSBC-32(E) is equipped with a VMEbus backplane interface connector.

The board is provided with a complete master interface for the VMEbus backplane connector. The VMEbus master interface consists of a VMEbus arbiter, requester, system controller and buffers for data/address/control signals. Simultaneously, the VSBC-32(E) can act as a VMEbus slave, as it is provided with a slave interface which consists of a programmable board address decoder, a dual-ported SRAM access and a mailbox interrupt controller.

To act as a system controller, the VSBC-32(E) is provided with arbiter, system clock driver, power monitor with system reset driver, IACK daisy chain driver and 7-level VMEbus interrupt controller.

Arbitration is single-level FAIR (compare VME64 Specification Rule 3.14/Observation 3.17) on BR3\*. If the VSBC-32(E) is used as a system controller, a special detection function provided by the board, which is also readable within the VMEbus control/status register, makes any "slot 1" jumper setting superfluous. The VMEbus interrupt acknowledgement is controlled via a daisy chain driver that is supplied with the board. IACK\* is connected via the VMEbus backplane for IACKIN\* of the system slot.

The signals SYSCLK\* and SYSRES\* can be routed from on-board to the VMEbus through the use of jumpers, leaving to the VMEbus user instead of the system controller the initiative of generating these signals. SYSFAIL\* generates a maskable on-board autovectored level-3 interrupt (please refer also to the section System Control Functionality (Interrupt Control) of this chapter), whereas ACFAIL\* generates a non-maskable on-board level-7 interrupt. The VSBC-32(E) also provides a bus monitor for the VMEbus. A 128µs bus error timer monitors the cycle lengths of the VMEbus data transfer and generates a VMEbus BERR\* signal on timeout. This timer is enabled and disabled via the VMEbus control/status register which contains also a timeout status bit in order to identify the bus errors generated by the bus monitor.

Exchange and retention of system relevant data from the VMEbus to the CPU/DMA and viceversa is provided by means of 256kB or 1MB of a 16-bit wide dual-ported SRAM which is backed-up using Gold Caps. Both the VMEbus users and the on-board CPU have access to the SRAM memory (upper 8kB, i.e. even Byte addresses).

#### Note...

The dual-ported SRAM cannot be accessed through its own VMEbus interface. A bus monitor timeout would result due to the fact that any access by the VMEbus to the DPRAM would be blocked as long as the VSBC-32(E) is bus master.

An external VMEbus master may interrupt the VSBC-32(E) by setting P\_IRQ5 ("mailbox interrupt pending") in the VMEbus control/status register. Seen from the VMEbus, the address of this dual-ported register is identical to the base address of the dual-ported SRAM (lower 8kB, i.e. odd Byte addresses).

#### Note...

All bits of the VMEbus control/status register can be read from the VMEbus, but only the bit P\_IRQ5 is read/write.

For a complete map of the VMEbus control/status register please refer to the relating section in the Configuration chapter of this manual.

For any general VMEbus information including generic pinouts please refer to Appendix B of the ANSI/VITA VME64 Specification.

#### 2.4.7 CXC Mezzanine Interface

The VSBC-32(E) is equipped with a CXC mezzanine interface connector.

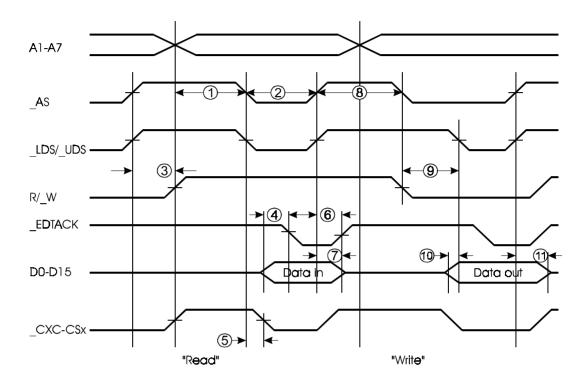

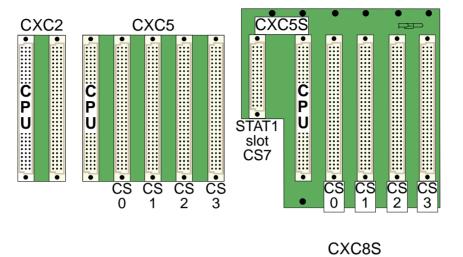

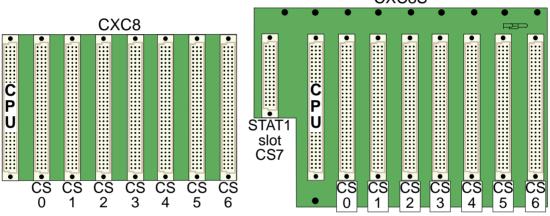

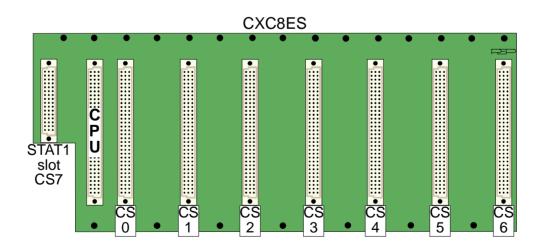

CXC and eCXC both contain a 16-bit data bus, seven address lines and eight decoded chip select lines. In total, there are eight control signals (CXC\_CS0...CXC\_CS7). The base address of the CXC can be programmed via the CS5 line of the MC68(EN)360. The main difference between the two VITA standards is the amount of address space available for peripheral devices:

- CXC: 8\*256Bytes (overall length: 0x400H, 1024Bytes actually available)

- eCXC: 8\*16MB (overall length: 0x1000 000, 16MB actually available)

Furthermore, the (e)CXC contains a 4-IRQ capability (4 edge-sensitive interrupt requests), DMA capability (1 channel, DREQ + DACK), serial ports (3 channels, Full MODEM) and a set of parallel port signals. These special CXC functions are based on the MC68(EN)360 controller resources.

For general CXC information, including generic pinouts and a comparison of the MC68(EN)360 and the MC68302 CPU pinouts on the CXC, please refer to the "CXC" appendix attached to this manual, the *PEP Modular Computers* CXC Reference Manual or to the CXC Specification.

#### 2.5 VSBC-to-VSBC-32 System Upgrading

In the following the porting information required by customers wanting to upgrade their VSBC-based systems to an VSBC-32 based one is supplied.

The VMEbus/CXC ports SER1, SER2 and SER3 of the MC68302 are equivalent to ports SCC2, SCC3 and SCC4 respectively on the MC68(EN)360 controller chip.

With regard to special VMEbus/CXC capabilities, the VMEbus/CXC pinout on the VSBC-32(E) has been developed to provide maximum compatibility between the standard VMEbus/CXC functions. In addition, all signals are available in order to configure two time division multiplexed channels via the VMEbus/CXC (ISDN, PCM, GCI and so on).

Multifunction pins with incompatible functions with regard to the MC68302 and MC68(EN)360, which are called "user-defined" in the generic CXC Specification, are not part of the VSBC-32(E) VMEbus or CXC specification.

Although the SMCs are configured on the mainboard, these ports are also integrated on the VMEbus/CXC because of possible ISDN applications where SMCs can be integrated and other protocols supported by the MC68(EN)360.

#### Note...

If the RCLK2 signal (VMEbus/CXM pin C16) is required, jumper J4 (24MHz clock) must be opened and the serial drivers delivered by *PEP Modular Computers* must be modified.

| CXC<br>Function | Pin | MC68302<br>HW<br>Comp. | MC68(EN)<br>360<br>Port | Comment                              | See<br>Note |

|-----------------|-----|------------------------|-------------------------|--------------------------------------|-------------|

| IRQ_1           | A1  | Yes                    | PC0                     | -                                    |             |

| IRQ_2           | A2  | Yes                    | PC1                     | -                                    |             |

| IRQ_3           | A3  | Yes                    | PC2                     |                                      |             |

| IRQ_4           | A4  | Yes                    | PC3                     | _                                    |             |

| DMA_ACK         | C2  | Yes                    | PB5                     | -                                    |             |

| DMA_REQ         | C3  | Yes                    | PB4                     |                                      |             |

| SER1_RCLK       | B1  | Yes                    | PA8                     | -                                    |             |

| SER1_TCLK       | B2  | Yes                    | PA10                    |                                      |             |

| SER1_TXD        | B4  | Yes                    | PA3                     | _                                    |             |

| SER1_RXD        | B10 | Yes                    | PA2                     | _                                    |             |

| SER1_RTS        | B5  | Yes                    | PB13                    | _                                    |             |

| SER1_DTR        | A13 | Yes                    | PB17                    | _                                    |             |

| SER1_CTS        | B13 | Yes                    | PC6                     | _                                    |             |

| SER1_CD         | B14 | Yes                    | PC7                     | _                                    |             |

| SER2_RCLK       | C16 | Yes                    | PA13                    | Cannot be used if J4 is set          | 3           |

| SER2_TCLK       | C15 | Yes                    | PA12                    | _                                    |             |

| SER2_TXD        | C17 | Yes                    | PA5                     | _                                    |             |

| SER2_RXD        | C18 | Yes                    | PA4                     |                                      |             |